Trước PLD, các bộ ghép kênh được sử dụng để thiết kế mạch logic tổ hợp, các mạch này rất phức tạp và cứng nhắc. Sau đó, các thiết bị logic lập trình (PLD) được phát triển và PLD đầu tiên là ROM. Thiết kế ROM không thành công lắm vì nó nổi lên vấn đề lãng phí phần cứng và tăng sự tăng trưởng theo cấp số nhân trong phần cứng cho mọi ứng dụng lớn. Để khắc phục những hạn chế của ROM, PLA và PAL đã được nghĩ ra. PLA và PAL được lập trình và sử dụng hiệu quả phần cứng.

Biểu đồ so sánh

| Cơ sở để so sánh | PLA | PAL |

|---|---|---|

| Viết tắt của | Mảng lập trình logic | Lập trình mảng logic |

| Xây dựng | Mảng lập trình của cổng AND và OR. | Mảng lập trình của cổng AND và mảng cố định của cổng OR. |

| khả dụng | Ít sinh sôi nảy nở | Sẵn có hơn |

| Mềm dẻo | Cung cấp sự linh hoạt hơn về lập trình. | Cung cấp ít linh hoạt hơn, nhưng nhiều khả năng được sử dụng. |

| Giá cả | Đắt | Chi phí trung gian |

| Số lượng chức năng | Số lượng lớn các chức năng có thể được thực hiện. | Cung cấp số lượng hạn chế của các chức năng. |

| Tốc độ | Chậm | Cao |

Định nghĩa của PLA

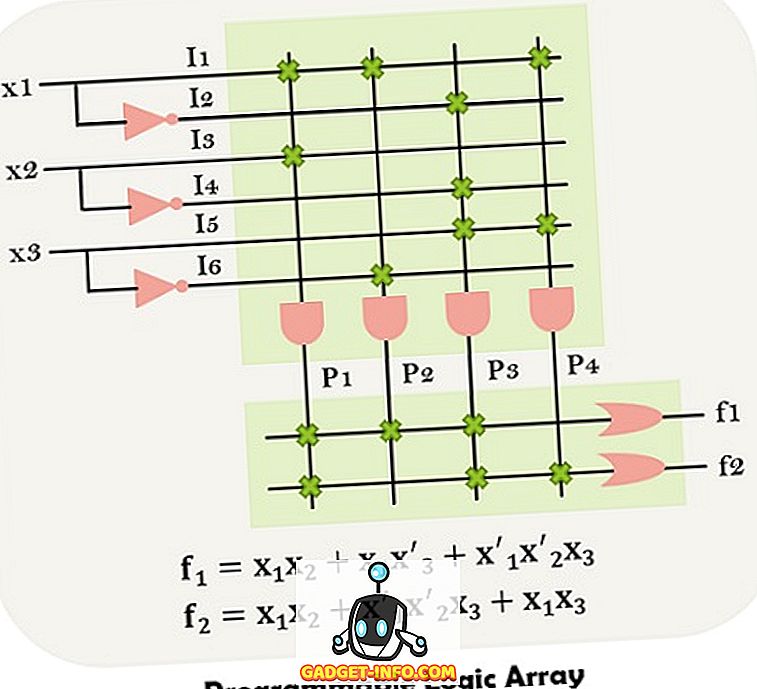

PLA là viết tắt của Mảng logic lập trình được biểu thị hàm boolean ở dạng SOP (Tổng sản phẩm). PLA chứa các cổng KHÔNG, AND và OR được chế tạo trên chip. Nó vượt qua mọi đầu vào bằng một cổng KHÔNG làm cho mỗi đầu vào và phần bổ sung của nó có sẵn cho mọi cổng AND. Đầu ra của mỗi cổng AND được cung cấp cho mỗi cổng OR. Cuối cùng, đầu ra cổng OR tạo ra đầu ra chip. Vì vậy, đây là cách các kết nối phù hợp được thực hiện để sử dụng các biểu thức SOP.

Trong PLA, các kết nối đến cả mảng AND và OR đều có thể lập trình được. PLA được coi là đắt hơn và phức tạp hơn so với PAL. Hai kỹ thuật sản xuất khác nhau có thể được sử dụng cho PLA để tăng tính dễ lập trình. Trong kỹ thuật này, mỗi kết nối được xây dựng thông qua một cầu chì tại mọi điểm giao nhau nơi các kết nối không mong muốn có thể được loại bỏ bằng cách thổi các cầu chì. Kỹ thuật thứ hai liên quan đến việc tạo kết nối tại thời điểm của quá trình chế tạo với sự trợ giúp của mặt nạ thích hợp được cung cấp cho mẫu kết nối cụ thể.

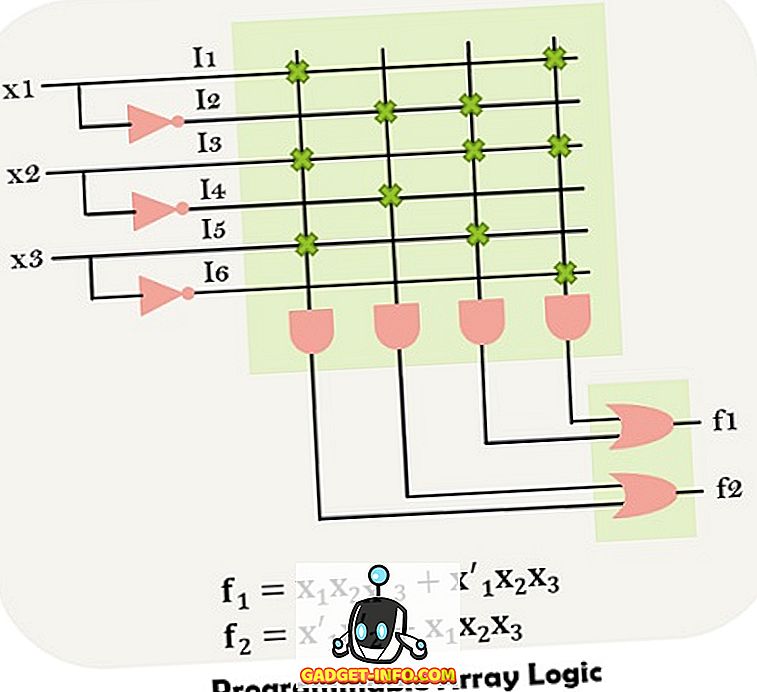

Định nghĩa của PAL

PAL (Logic lập trình mảng logic) cũng là mạch PLD (Thiết bị logic lập trình được) hoạt động tương tự như PLA. PAL sử dụng các cổng AND có thể lập trình nhưng các cổng OR cố định, không giống như PLA. Nó thực hiện hai chức năng đơn giản trong đó số lượng cổng AND được liên kết với mỗi cổng OR chỉ định số lượng điều khoản sản phẩm tối đa có thể được tạo trong biểu diễn tổng sản phẩm của chức năng cụ thể. Mặc dù các cổng AND được kết nối vĩnh viễn với các cổng OR, điều này biểu thị rằng thuật ngữ sản phẩm được sản xuất không thể chia sẻ được với các chức năng đầu ra.

Khái niệm chính đằng sau việc phát triển PLD là nhúng logic boolean phức tạp vào một chip đơn. Do đó, loại bỏ hệ thống dây không đáng tin cậy, ngăn chặn thiết kế logic và giảm thiểu tiêu thụ điện năng.

Sự khác biệt chính giữa PLA và PAL

- PLA là PLD, bao gồm hai cấp độ logic lập trình AND và mặt phẳng OR. Mặt khác, PAL chỉ chứa mặt phẳng AND có thể lập trình và mặt phẳng OR cố định.

- Khi có sẵn, PAL sẵn sàng hơn cùng với việc sản xuất dễ dàng. Ngược lại, PLA không dễ dàng có sẵn.

- PLA linh hoạt hơn PAL.

- PLA đắt hơn so với PAL.

- Một số hàm do PLA cung cấp tương đối nhiều hơn vì nó cũng cho phép lập trình mặt phẳng OR.

- PAL hoạt động nhanh hơn trong khi PLA tương đối chậm hơn.

Phần kết luận

Mảng lập trình logic (PLA) và Mảng lập trình lập trình (PAL) là PLD (Thiết bị logic lập trình) trong đó PLA có khả năng thích ứng và linh hoạt hơn PAL. Tuy nhiên, PAL có thể dễ dàng tạo ra một mạch logic kết hợp.